Get the latest tech news

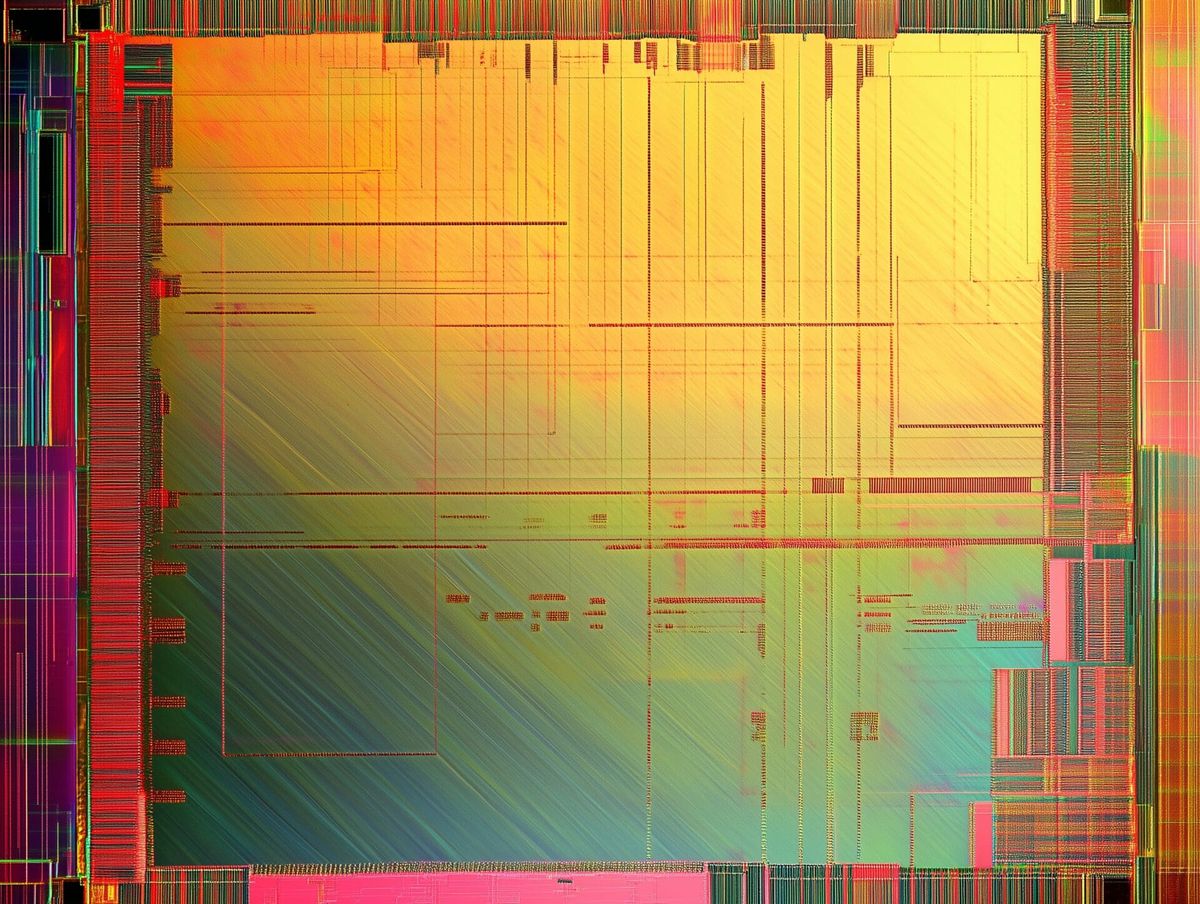

A FPGA friendly 32 bit RISC-V CPU implementation

A FPGA friendly 32 bit RISC-V CPU implementation. Contribute to SpinalHDL/VexRiscv development by creating an account on GitHub.

The following numbers were obtained by synthesizing the CPU as toplevel on the fastest speed grade without any specific synthesis options to save area or to get better maximal frequency (neutral). ParameterstypedescriptionearlyBranchBooleanBy default the branch is done in the Memory stage to relax timings, but if this option is set it's done in the Execute stagecatchAddressMisalignedBooleanIf a jump/branch is done in an unaligned PC address, it will fire an trap exceptionEach miss predicted jumps will produce between 2 and 4 cycles penalty depending the earlyBranch and the PcManagerSimplePlugin.relaxedPcCalculation configurations The downside is that this predictor has a long combinatorial path coming from the prediction cache read port to the programm counter, passing through the jump interface.

Or read this on Hacker News