Get the latest tech news

Memory Mapping an FPGA from an STM32

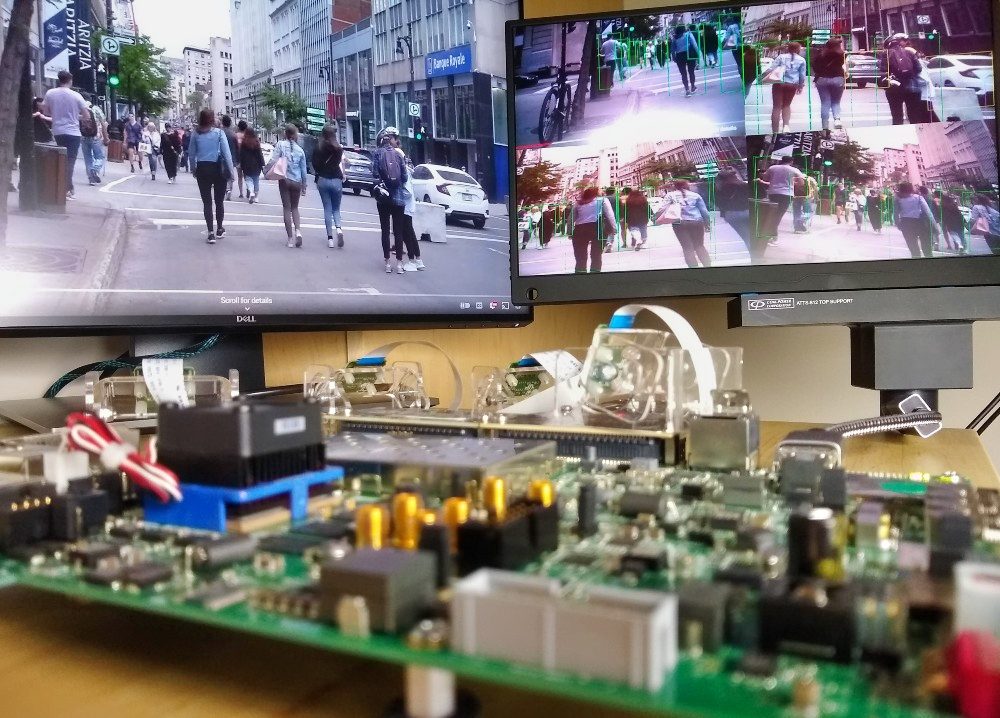

I teased at this a bit in my previous posts and finally have a setup I’m happy with, so I thought I’d do a more in-depth writeup. To recap, the planned architecture for most of my future large-scale embedded projects is a fairly large (AMD Xilinx Kintex-7 or Artix / Kintex UltraScale+) FPGA for the high speed data plane paired with a STM32H735 for the control plane with a memory mapped interface between them.

Using a MCU-class Cortex-M CPU instead of an applications processor is simpler to program in a bare-metal no-OS or minimal RTOS environment The large (564 kB) on chip SRAM and 1 MB on chip flash eliminates the need for time-consuming DDR SDRAM layout for my typical firmwares (<200 kB each of ram/flash used) The disaggregated pinout (two smaller BGAs rather than one larger one) is simpler to fan out on less PCB layers, and allows placing the FPGA and MCU with some distance between them if this is more convenient for layout reasons Decentralizing allows the FPGA and MCU to enforce security boundaries between each other. APB latency is properly propagated back to the NWAIT signal on the FMC, so peripherals can take arbitrarily long to service requests (although this will stall the AXI bus on the STM32, so beware). On my next “real” design I’ll have a faster FPGA (although potentially slower IOs, UltraScale+ HDIO are actually somewhat slow compared to 7 series HR) and may spend some time playing with constraints and PLL phases to see if I can push it any further.

Or read this on Hacker News