Get the latest tech news

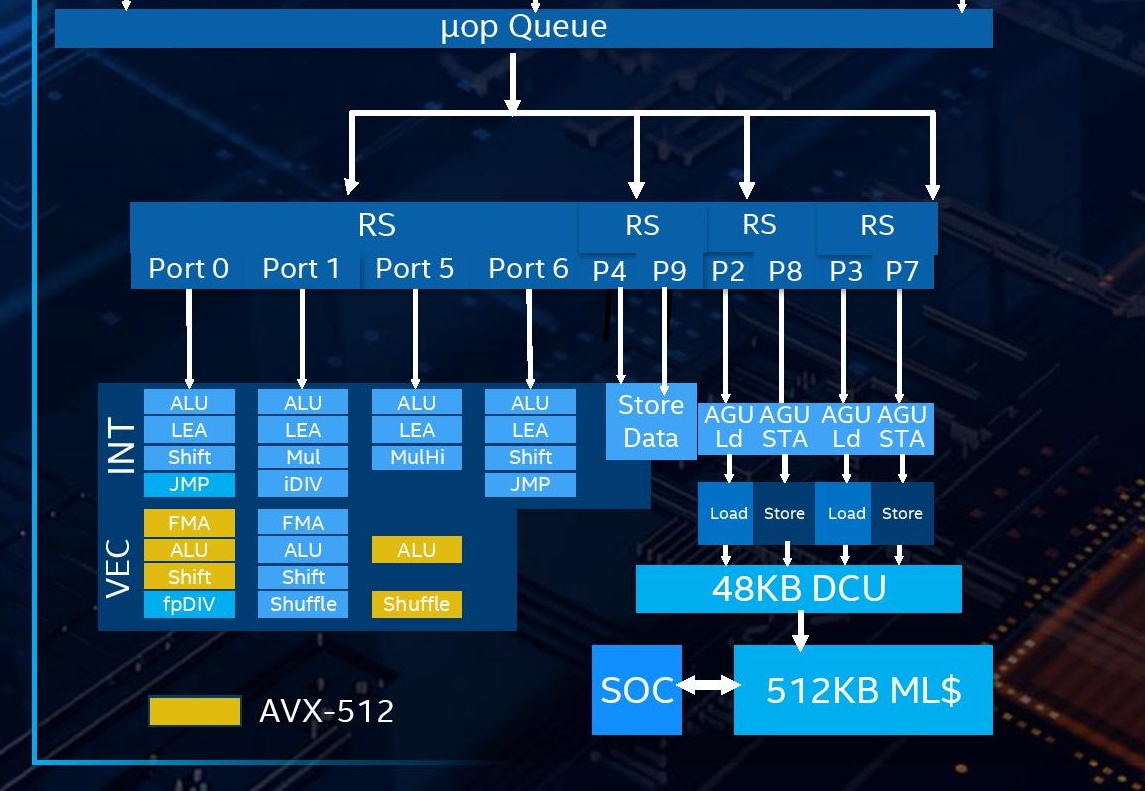

Zen5's AVX512 Teardown and More (Without Redacted Content)

By Alexander J. Yee (@Mysticial) (Last updated: August 14, 2024) Shortcuts: This article was supposed to be published all at once on July 30'th.

In fact, the AVX512 improvement on Zen5 created a memory bottleneck so large that it became the primary reason why I promoted the BBP mini-program from a tool for verifying Pi records to a formal benchmark. Slapping on high-end coolers like tower heatsinks or 360 AIOs wouldn't change that since it simply allowed the CPU to boost higher and get back to 95C. Rather than stalling the execution for the ~50,000 cycles needed to do this transition, Intel CPUs will break up the wider instructions and "multi-pump" them into the hardware that is already powered on and ready (and safe) to use at the current clock speed.

Or read this on Hacker News